半导体所半导体超晶格国家重点实验室高速图像传感及信息处理课题组的张钊研究员等研制出一款极低电压、低抖动低功耗频率综合器芯片。相关研究成果以题目为“0.4V-VDD 2.25-to-2.75GHz ULV-SS-PLL Achieving 236.6fsrms Jitter, -253.8dB Jitter-Power FoM, and -76.1dBc Reference Spur”的论文发表在集成电路芯片设计领域的顶级会议IEEE International Solid-State Circuits Conference(ISSCC)上。

物联网系统需要同时具有低抖动和低功耗的频率综合器,以满足低功耗高质量无线数据收发的需求,且提高无线传感器等设备的待机时间,而降低电压是降低功耗的有效技术路线。课题组提出了一种新型的频率综合器的系统架构和极低电压电路的噪声降低技术,有效降低了低抖动锁相环的电压和功耗,并通过流片验证了提出的新技术的有效性。

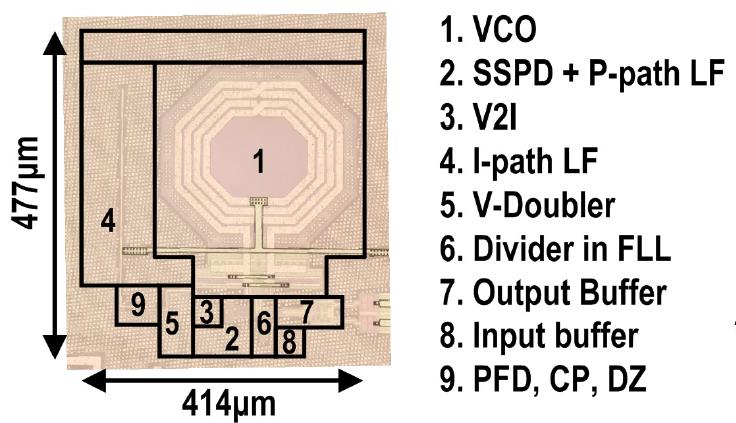

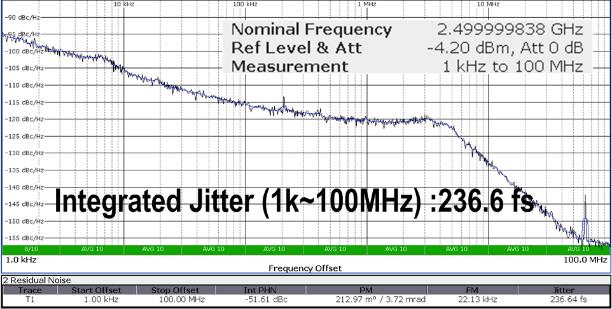

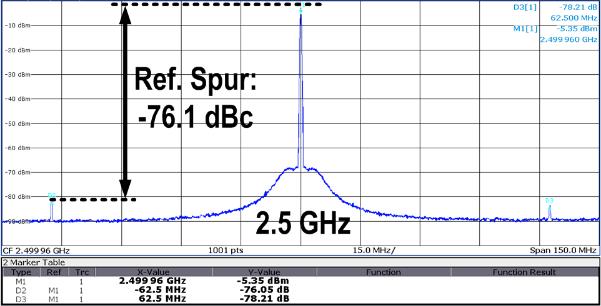

该频率综合器芯片包含如下新技术:提出了一种全新的三通路架构,显著提升在极低电压下压控振荡器的频率调谐范围,从而减小低电压振荡器的设计复杂度,降低电路功耗;提出一种基于无源缓冲器隔离技术的亚采样鉴相器,能够在极低电压下保持足够鉴相器增益,从而获得低带内相位噪声,实现极低电压下的低抖动性能。测试结果表明,该芯片能够在0.4 V电压下正常工作,积分抖动低至236.6 fs,且功耗仅为0.74 mW;同时,频率覆盖范围为2.25-2.75GHz,参考杂散为-76.1dBc。图1和图2分别为芯片照片和测试的输出的积分抖动和参考杂散结果。

该工作获得国家自然科学基金项目和北京市科技计划项目的支持,澳门大学为该项工作的合作方。

图1 芯片照片

图2 关键测试结果