基于有意时钟偏差的单环无参考时钟与数据恢复电路

随着数据传输业务量的日益增长,高速串行器-解串器(SerDes)接口的功耗问题已成为制约其发展的瓶颈之一。作为SerDes接口的重要组成部分,时钟与数据恢复电路(CDR)能量效率的提升同样迫在眉睫。其中,无需外部参考时钟源的CDR电路因其低成本与宽范围而受到广泛关注。其主要挑战在于仅依靠伪随机性数据实现稳定、快速、宽频率范围的时钟恢复。

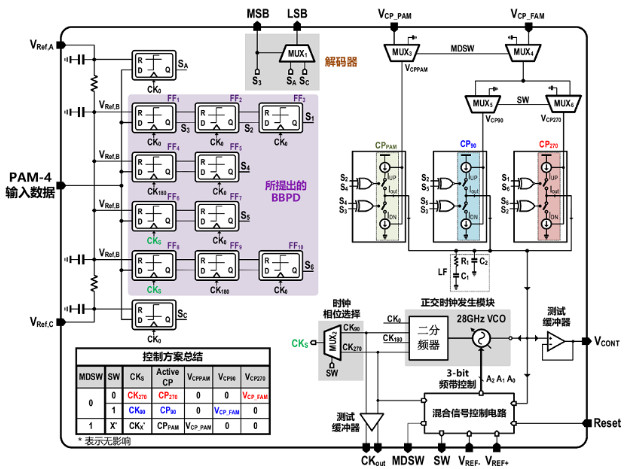

针对上述挑战,澳门大学陈勇副教授团队提出了基于有意时钟偏差的无参考频率捕获方案,如图1所示。在传统全速率的二进制鉴相器(BBPD)中,连续三点采样的中间点采样时钟(CKS)与其余两采样时钟相位相反,其鉴相特性曲线关于原点对称,频率捕获能力有限。所提出的方案有意地为CKS引入偏移量(Strobe Point),从而获得单向的频率捕获能力。结合所提出的算法,所提出的CDR,在具有频差时,可自动搜索进入正确的频带,最终回归于正常锁定。该方案采用紧凑、低功耗的正交时钟方案以优化能量效率;无需数据采样时钟,因此适用于PAM-4信号制式;同时以单环的架构规避了双环路的环路切换引起的稳定性问题。

图1. 提出的无参考CDR的完整原理图及其控制总结。

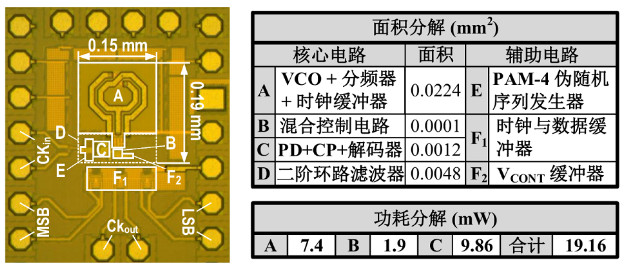

基于上述技术,陈勇副教授团队采用 28nm CMOS 工艺以紧凑的核心面积(0.0285 mm2,如图2所示,在无需鉴频器硬件下,实现了自动频率捕获和同期领先的能量效率(0.68 pJ/bit)并大幅提升频率捕获速度[8.2 (Gb/s)/μs]。

图2. 芯片照片与面积、功耗分解。

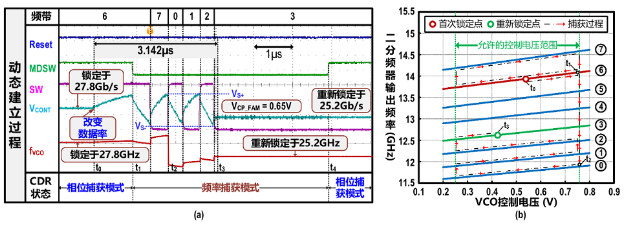

图3(a)显示了测试的动态频率捕获过程。最初,CDR已锁定于VCO的第6个子频带。t0时刻,数据率发生突变,VCO控制电压上漂,在t1时刻超过上限阈值,从而激活频率捕获模式。得益于控制算法中的循环计数器,所提出的CDR搜索5个子频带后重新实现锁定。图3(b)展示了在VCO调谐全范围内的对应频率搜索过程,实现了由高数据率向低数据率的锁定,这表明在负的频差极性下,所提出的环路依然可以自动完成频率捕获。

图3. (a)切换数据率后自动频率捕获的动态过程实测结果; (b)呈现在VCO调谐范围内的相应频率变化过程。

本工作创新性地将本应避免的时钟偏差用于解决频率捕获难题。所提出的CDR技术实现面积小,捕获速度快,鲁棒性强,为多标准、多频带的高速SerDes芯片小型化、低功耗化提供了新的技术方案。且理论分析表明所提出的技术可拓展应用于更高的数据率。

相关研究成果于2022年2月以"A 0.0285-mm2 0.68-pJ/bit Single-Loop Full-Rate Bang-Bang CDR without Reference and Separate FD Pulling off an 8.2-Gb/s/μs Acquisition Speed of the PAM-4 Input in 28-nm CMOS" 为题发表于集成电路领域国际顶级期刊IEEE Journal of Solid-State Circuits (JSSC)。澳门大学博士研究生赵潇腾为论文第一作者。陈勇副教授为论文通讯作者。

来源:半导体学报公众号