放大后残差生成单通道 3.3-GS/s 6-b 全动态流水线型模数转换器

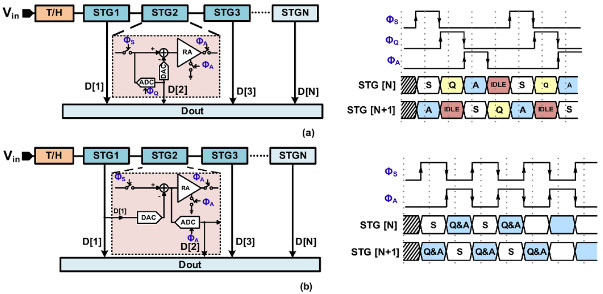

GHz量级采样频率的低功耗模数转换器(ADC) 是数字通信系统的关键器件。逐次逼近型ADC具有能效高的优点,但即使使用多位转换、两步、替代比较器或循环展开等技术,其单通道采样频率很难提升到1.5GHz以上;时间交错逐次逼近型ADC因受到偏移和增益失配以及通道之间采样时钟偏差的影响,需要进行复杂校准计算来补偿;闪存ADC具有速度快和延迟小的特点,但它也带来了高功率、大输入电容和反冲,即使使用折迭或插值技术,仍然无法改善功率大或校准电路开销大的问题;流水线架构通常用于具有 9~12 位分辨率和每通道每秒2GHz左右的中等采样率的 ADC,流水线的每个阶段必需完成采样、量化和残差放大操作,限制了整体转换速度。并且传统的死循环残差放大器存在需要高增益、稳定性差和功耗大的问题。动态放大器可以提高功率效率和速度,但由于输入依赖共性电流,特别是在大输入摆幅下,线性度相对较差。

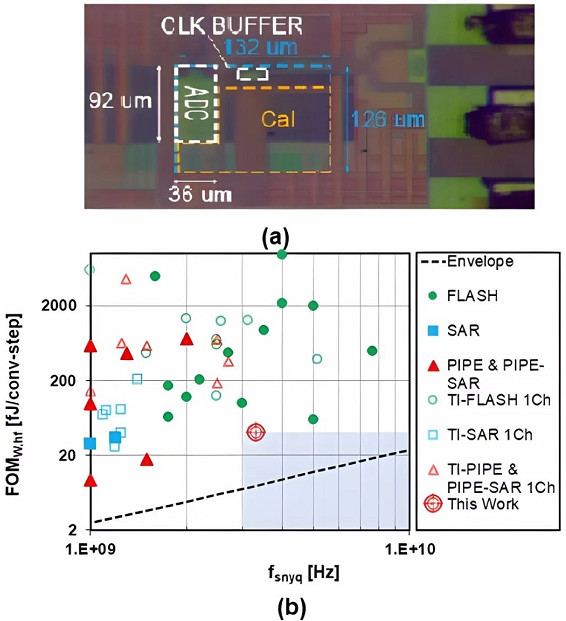

澳门大学陈知行教授课题组通过分析和改进流水线型ADC的传统采样、量化和放大的串行工作流程,提出了一种量化和放大同时并行处理的放大后残差生成的ADC架构,每一级的残差由电容数模转换器产生并由动态放大器放大,可以实现高速和低功耗的处理。提出的辅助补偿技术可以有效地提高放大器的线性度,通过额外引入的电流支路实现高的补偿效率并只对带宽产生非常轻微的影响。基于提出ADC架构,实现了一款放大后残差生成单通道全动态流水线型模数转换器,具有结构简单、硬件开销小和片上校准的优点。图2给出了3.3 GHz采样率单通道全动态流水线型ADC的照片和比较结果。它通过奈奎斯特输入和大于6 GHz的有效分辨率带宽实现34 dB 信噪失真比(SNDR)和45 dB无杂散失真比(SFDR),在0.9 V电源下消耗5.5 mW,面积仅为0.0166 mm2,是目前流水线型ADC单通道中最高速的设计。

图 1. (a) 传统的流水线型 ADC 架构和时序图,(b) 提出的放大后残差生成方案的流水线型ADC。

图 2. (a) 芯片显微照片,(b) 跟前沿ADC比较。

该工作以题为“A 3.3-GS/s 6-b Fully Dynamic Pipelined ADC With Linearized Dynamic Amplifier”发表在IEEE JOURNAL OF SOLID-STATE CIRCUITS期刊(2022, 57(6): 1673-1683)。澳门大学陈知行教授是该工作的通讯作者,郑子豪是第一作者,主要指导老师还包括澳门大学诸嫣教授,合作方是来自比利时校际微电子中心的Ewout Martens博士和Jan Craninckx博士等。该工作突破了传统流水线型模数转换器的工作时序限制,实现了单通道中最高速的流水线型模数转换器,有望进一步减少有线通讯中接收器的面积及功耗。

该工作得到了澳门科学技术发展基金与国家自然科学基金委员会联合科研资助 (编号:0003/2019/AFJ)。

来源:半导体学报微信公众号