一款内嵌无参考时钟CDR的26-Gb/s CMOS光接收机芯片系统

在高速高密的通信应用中,由于传统的电互连方案在成本、能量效率、信道带宽(BW)、串扰(XT)和电磁干扰(EMI)等方面渐渐失去了竞争力,其替代方案一短距光互连方案已经崭露头角。与其他III-V族化合物技术(如基于GaAs、InP的设计)相比,基于互补金属氧化物半导体(CMOS)的光电集成电路(OEICs)能以极低的制造成本和更高的集成度广泛地应用于高速通信。因此,基于CMOS的光互连可作为下一代云计算和大数据应用的一个富有潜力的候选方案。

近日,南方科技大学潘权教授课题组设计并测试验证了一款基于65 nm CMOS的速率为26-Gb/s的CMOS光接收机,包括一个光接收前端和一个内置12-dB均衡的无参考的全速率时钟和数据恢复(CDR)电路,目标是用于100GbE光通信。

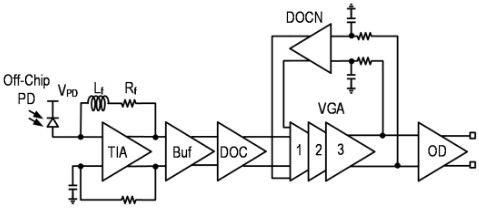

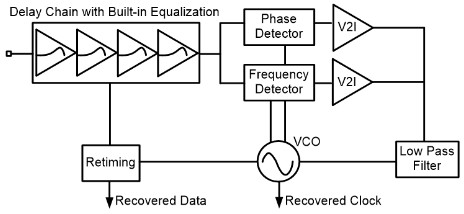

本设计的亮点首先在于设计了一个基于反相器的三电感峰化的伪差分TIA。采用并联峰化反馈电感(Lf)和输入串联峰化电感(Ls)对电路的带宽进行扩展。同时后级连接的基于电流模逻辑(CML)的TIA缓冲级,既能起到直流电平偏移的抑制作用,又能缓解差分输出的失配,以增强DOC级直流电压偏移消除能力。这种基于反相器的TIA加TIA缓冲器的拓扑结构相较于传统的TIA结构,可以实现更好的跨阻增益,更高的带宽,以及更少的直流偏移失配。其次,为了减轻工艺、电压和温度的偏差带来的影响,VGA的增益和负载网络是由一个00000到11111的5位数字控制,从而补偿整个前端的增益变化以提供足够的摆幅驱动CDR。最后,在CDR中设计了均衡延时单元,均衡延时单元可以在不改变延时特性的同时提升高频增益。为了节省CDR的面积,此设计使用了堆叠电感技术,在未来的研究中,该技术还可以用于光前端设计,进一步减小芯片面积。该CDR还使用了相位和频率检测环路,使得时钟恢复不需要参考时钟,减轻了传输线的布局压力。芯片最终的测试结果表示,与其他采用光前端和CDR的工作相比,该工作在能量效率和恢复的时钟抖动方面都有显著提高。

图1. 光接收机前端模块图。

图2. 光接收机前端模块图图2 内置均衡的无参考时钟与数据恢复电路。

文章信息:

A 26-Gb/s CMOS optical receiver with a reference-less CDR in 65-nm CMOS

Quan Pan, Xiongshi Luo, Zhenghao Li, Zhengzhe Jia, Fuzhan Chen, Xuewei Ding, C. Patrick Yue

J. Semicond. 2022, 43(7): 072401

doi: 10.1088/1674-4926/43/7/072401

Full Text: http://www.jos.ac.cn/en/article/doi/10.1088/1674-4926/43/7/072401

来源:半导体学报2022年第7期-中文导读