成功实现二维半导体集成电路成套工艺

人工智能和可移动终端的迅猛发展,导致对芯片高算力和低能耗的要求越来越高。目前集成电路最先进的晶体管沟道长度和厚度开始逐步接近原子尺度,而传统半导体材料已经接近性能极限。最新的国际器件与系统路线图(IRDS)指出,具有原子厚度的二维半导体在未来大规模集成电路中有巨大的潜力。所以,发展基于二维半导体的新型芯片具有极其重要的战略意义。当前国际上大面积二维半导体的生长已经有诸多报道,但是其集成电路应用仍在探索初期。主要困难是原子级厚度的二维半导体对工艺环境极端敏感,所以传统半导体CMOS集成工艺不能直接用来照搬。这就需要工业界和学术界共同投入大量的精力来开发基于二维半导体的新型集成电路工艺。

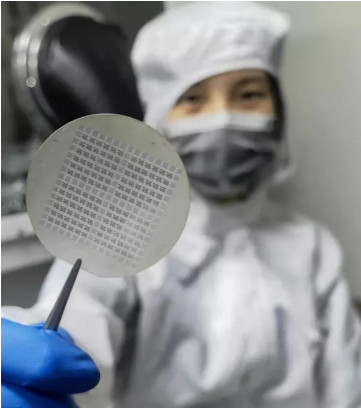

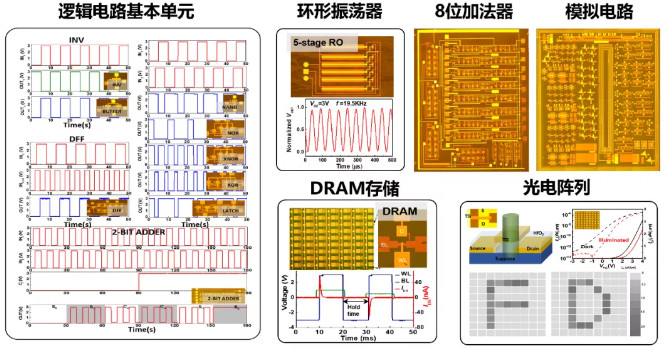

复旦大学微电子学院的包文中研究员课题组和周鹏教授团队近年来长期合作,聚焦于新型二维半导体材料的集成电路应用,在材料晶圆级生长、工艺集成、电路设计等方向系统开展了深入的研究工作,已经取得了一定的积累。在此工作中,科研团队利用已经积累的较大实验数据样本集,采用机器学习算法训练并识别具有优良器件指标的器件工艺特征,辅助优化了二维半导体增强型顶栅晶体管的制备工艺。最终极大程度地缩短了二维材料集成电路成套工艺探索进程,大幅提高了科研人员的研究效率(图1)。最后基于此工艺采用工业标准设计流程和工艺进行了晶圆级器件与电路的制造和测试,成功演示了各种数字、模拟、存储、光电探测等集成电路单元(图2)。从而展示了未来二维材料体系芯片应用的光明前景。

这项研究工作的核心内容是就是利用机器学习的高效性来辅助科研人员进行巨量组合的筛选优化,提出了一种适合学术界探索的二维半导体集成电路工艺优化路线。而且本工作所采用的机器学习策略具有通用性,其他新型材料也可以利用此策略缩短其器件工艺探究与应用进程,大幅减少科研人员的重复工作从而提高科研效率。研究团队未来将继续聚焦于新型二维半导体,深挖其特有属性,往新计算范式、三维集成应用方向探索,进一步推动其在集成电路产业中的实际应用。

研究成果于2021年10月12日以“Wafer-scale functional circuits based on two dimensional semiconductors with fabrication optimized by machine learning”为题发表在《自然?通讯》(Nature Communications, 2021, 12, 5953)杂志上,解玉凤教授、博士生陈新宇、硕士生盛耀晨和唐宏伟为共同第一作者,包文中、万景研究员和周鹏教授为共同通讯作者。该工作同时还与上海市微系统所、香港理工大学、新加坡国立大学、苏州大学、深圳六碳科技等兄弟单位紧密合作,并得到了科技部重点研发计划纳米科技专项、国家自然科学基金杰出青年和应急重点项目、上海市教委科研创新重大项目等项目的支持。

图1. 二维半导体的算法辅助工艺优化、顶栅工艺结构以及晶圆级流片结果。

图2. 利用优化的二维半导体顶栅工艺制作的各种常见集成电路单元。