功耗感知的功耗平衡和掩码方法混合运用实现低开销抗功耗攻击S盒

功耗攻击可以通过分析密码芯片加/解密过程中电源电流的变化轨迹获得加密算法的密钥。类似的原理还可以用于电磁辐射分析攻击。这些攻击都属于侧信道攻击,它们利用的是密码芯片的物理特征和运算中间结果之间的相关性,可以绕过密码算法安全性所基于的数学难题,直接得到密钥信息,是密码芯片的重要威胁之一。

为了应对侧信道攻击,研究人员设计了多种防护手段。这些手段中很重要的两种思路是掩码方法和隐藏方法。掩码方法的思想是在不改变运算结果的前提下使得运算过程中产生的中间结果是随机的,这样,它们所产生的功耗等物理特征将变得随机,和密钥不再相关。掩码方法的具体做法是引入随机数(掩模)参与运算,在最终结果输出前再把掩模的去除,恢复原始数值。隐藏方法的思想是不改变中间结果,而是降低所产生的物理特征的信噪比,使得功耗等物理特征和中间结果不再相关。实现隐藏方法的一个重要途径是实现功耗平衡,也就是让计算不同数据所产生的功耗都是相同的。另一条隐藏的途径是增加物理特征的噪声。掩码方法和隐藏方法在学术界和工业产品中都有广泛应用,具体的实现技术也非常丰富。

虽然上述两种方法都可以防护侧信道攻击,但是也带来了密码芯片的额外开销。掩码算法在用于非线性运算时计算复杂度往往大幅提升,带来了面积、延时、功耗的开销。隐藏方法为了实现所有情况下的功耗都是相等的,只能增加低功耗情况下的运算功耗,让功耗和最坏情况一致,这必然带来额外的功耗开销。增加噪声的方法也是一种增加冗余功耗的方法,噪声幅度和功耗增加的幅度成正比,高安全性意味着高功耗。随着物联网的普及,物联网安全日益重要,物联网节点也要配备加密运算模块,而大部分物联网设备对硬件功耗或硬件的能量效率(工作频率和功耗的比值)都有较高要求,所以,传统的掩码方案和隐藏方案无法满足物联网设备的要求。在这样的背景下,低功耗的功耗分析攻击防护技术对于物联网而言就具有了重要意义。

清华大学微电子学研究所李翔宇副研究员课题组为了解决传统功耗平衡技术的功耗开销问题提出了一种功耗感知的功耗平衡技术(Power-Aware Hiding, 缩写成PAH)。它是针对分组密码算法中的S盒提出的安全实现技术,具有能量效率高、支持半定制设计流程的优点。S盒是很多分组密码算法的核心计算,是一种高度非线性的双射置换运算。PAH的基本思想是根据运算电路的输入输出预先计算出电路的翻转功耗,然后通过数据编码和补偿适当功耗相结合的方式实现功耗平衡效果,使得最终平衡的功耗等于一个预设值,该值理论上只有原始设计电路峰值功耗的一半。ASIC实现中操作的功耗大致上与寄存器数据的汉明距离(Hamming distance, HD)成正比,保持固定的汉明距离是功耗平衡的主要方面。功耗感知的功耗平衡技术通过补偿平衡输出数据的汉明重量(Hamming weight, HW)和在两个连续状态的有效数值之间插入间隔态,即对寄存器进行预充电的方式,来实现固定的输出汉明距离。

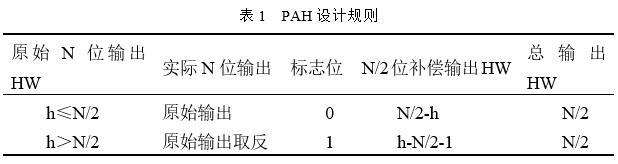

表1是功耗感知的功耗平衡技术的设计规则,该方法假设一个运算原始的输出是N位的,如果原始输出的汉明重量h不大于输出位数的一半即N/2时,实际输出就等于原始输出;而当原始输出的汉明重量h大于N/2时,实际输出的值等于原始输出取反,这种设计规则的一个直接结果是实际输出的汉明重量总会小于N/2。为了得到运算的原始输出,该方法增加了一个标志位f。额外增加的N/2比特补偿位用于将实际输出整体的汉明重量固定为N/2。

因为PAH的计算方法可以映射成查表过程,所以PAH方法在实现时可以采用类似可编程阵列逻辑的晶体管阵列。这种电路结构规则,具有较高的面积效率和较小的寄生效应,容易实现高的能量效率和好的电路匹配。实验证明PAH方法用于AES和SM4等密码算法的S盒“功耗延时积”可以降低70%多,同时功耗的差分也优于很多经典功耗平衡逻辑。但是,PAH方法也有一个非常明显的缺点——面积开销很大。这一缺点限制了它在成本敏感型的应用中的使用。

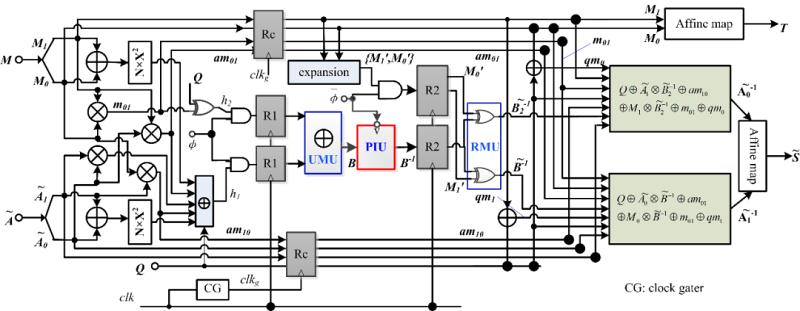

于是李翔宇课题组提出了一种改进的基于PAH的AES算法S盒电路结构。这种新的结构采用塔域的计算方法计算S盒。所谓塔域的计算方法是利用了如下的数学关系:AES S盒可以分解为GF(28)域上的求逆运算和仿射变换。GF(28)域中的元素的二进制表示是一个8位数,可以看作由2个4位二进制数组成。GF(28)域上的求逆运算可以转换成两个GF(24)的运算,其中包括GF(24)域上的求逆运算和加法、乘法、平方等。其中最为复杂的是GF(24)域上的求逆运算采用类似的分解方法,又可以用GF(22)域上的运算来计算。这种分解的好处是计算逻辑规模比8位数的查找表小很多。新结构利用塔域分解把GF(28)域的求逆运算变成了GF(24)域上的求逆运算和一系列简单的线性运算。线性运算的优点是可以以较小的代价实现掩码方案。PAH的优点是非线性运算的实现效率更高。塔域分解后,S盒运算的非线性运算规模变小了——由原来的8位置换表变成了4位置换表,规模减小了24倍。于是,新的改进S盒把掩码技术与PAH技术混合运用。采用PAH技术求GF(24)乘法逆元同时对其他模块进行掩码保护。新的S盒结构如下图所示。图中核心的PIU模块就是用PAH方式实现的GF(24)求逆单元。在PIU的前后各有两级流水线,对应GF(24)求逆之前和之后的其它运算,这些运算采用掩码方案(与经典的塔域AES S盒方案一种)。因为PAH不能在被掩码数据上使用,所以,在数据进入PIU之前要把掩模去掉——这对应图中的UMU模块(去掩模单元),然后,在完成求逆之后,要进行带掩码的计算,还需要给求逆结果加上掩模,所以在PIU之后有一级异或逻辑,把逆元和掩模异或(图中标为RMU,即重新掩码单元)。

改进后的方案相比之前的方案,因为PAH阵列的规模变小了,安全性更高,面积显著减小。

李翔宇课题组提出的新方案还针对掩码逻辑部分存在的毛刺会引起信息泄露的问题,提出了一种基于延时匹配的逻辑门翻转同步技术。毛刺产生的原因是同信号经过不同延时的路径重新汇聚到一个逻辑门。它产生与否和路径上的其它信号的取值有关,而毛刺会带来功耗的变化,所以会引起信息泄露。根据这一原理,新方案采用经过延时匹配的使能信号作为逻辑门翻转的同步信号,避免了提前翻转引起的信号毛刺。下图就是一条使能路径的电路图,图中标方框的逻辑级联构成一个可能产生毛刺的异或门链,但本图中的异或门是经过改造的带有使能端的异或门——它只有使能信号有效时才会翻转。图中灰色的逻辑门即是一条匹配延时链,用来控制异或门的使能信号的翻转时间,它保证每个异或门只有两个输入信号都到达后才翻转。采用这一措施后,掩码部分的毛刺可以被消除,安全性得到了提高。

课题组使用中芯国际180 nm CMOS工艺实现了上述电路并进行了仿真评估,评估结论是该S盒的一次运算消耗的能量是26.87 pJ, 面积是2,365等效门。它的能量是全掩码方案的17.6%,面积是全PAH的方案的61.2%,而且安全性也高于上述两种方案。这一结果显示了混合运用不同防护策略的优势。

综上所述,本文方法通过把非线性的S盒运算进一步分解为非线性和线性运算,线性运算采用线性运算实现效率高的掩码方案保护来控制电路的规模和设计复杂度,非线性运算则采用实现查表运算更高效的PAH方案来保护来控制电路的延时和功耗。这样的优化配置方案为低功耗高安全的侧信道防护技术提供了一种新的解决思路。该方法可以推广到其它密码算法的S盒设计中,解决物联网芯片安全和效率之间的矛盾。

Side-channel attack-resistant AES S-box with hidden subfield inversion and glitch-free masking

Xiangyu Li, Pengyuan Jiao, Chaoqun Yang

J. Semicond. 2021, 42(3): 032402

doi: 10.1088/1674-4926/42/3/032402

Full Text: http://www.jos.ac.cn/article/doi/10.1088/1674-4926/42/3/032402?pageType=en