基于VCO比较器振荡数的自适应多旁路窗在SAR ADC中的应用

模数转换器(ADC)是模拟集成电路的核心问题之一,也是我国“卡脖子”的重大需求领域。近年来,逐次逼近(SAR)型ADC由于其高度数字化、功耗低、可并行等特点,在先进工艺下得到了长足的发展,并在高速领域逐步取得明显的优势。但受制于器件匹配,SAR ADC的高精度设计一直是个难题。而低功耗、低延迟、中高精度的ADC在传感器和自动控制系统中扮演着不可或缺的角色。

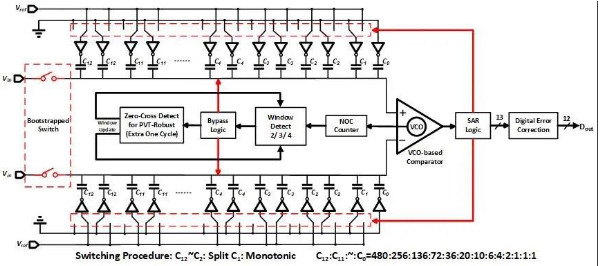

随着半导体工艺技术的发展,先进CMOS 工艺的特征尺寸与最大供电电压均在逐年下降。数字电路在功耗和工作速度方面相对较模拟电路在先进CMOS 工艺中获得了非常大的优势。对于模拟电路来说,特征尺寸的减小会导致CMOS 管的本征增益降低,低电压会带来噪声与电压裕度问题。因此数字化模拟电路成为了一个热门的研究领域。因为比较器是电荷重分配SAR ADC 系统中唯一的模拟电路,所以将电压域的比较器替换成时间域的电路就能实现SAR ADC 的数字化。VCO比较器可以将电压差异转化为时间差异,如果输入信号电压差较大,则基于VCO 的比较器仅需要消耗少量的能量就能得出比较结果;如果输入信号电压差较小,则该比较器可以实现低噪声的性能。基于VCO 的比较器在得出比较结果的时候,其所需要消耗的振荡周期数与输入信号的电压范围有一定的关系。

电子科技大学低功耗集成电路与系统研究所李强教授团队首先利用随机过程理论对VCO比较器的噪声特性进行了理论分析,得到闭环VCO比较器行为的解析解,发现VCO比较器会因为噪声原因而在没有达到足够多的振荡次数之前停止振荡,会降低比较器的噪声性能。VCO比较器每一个不同的振荡次数均对应一个不同的电压范围,但此对应关系对PVT敏感,自适应旁路窗技术则是通过窗宽度检测技术得到在PVT变化的情况下的合适的旁路窗,使系统可以跳过正确的逐次逼近周期数。在较高速的高精度ADC中,参考电压的变化会导致错误的输出,为了避免使用过大面积的片上去耦电容来稳定参考源,论文提出一种用于旁路窗逻辑的分裂-重组冗余算法来纠正错误的结果。

本论文展示了一款12-bit 30-MS/s的SAR ADC,使用40nm CMOS工艺进行了仿真,在30MS/s 采样率、1.1V 供电电压以及tt corner 下的总功耗为0.38W,SFDR 达到85.35dB,ENOB 为11.12 位,品质因子为5.69 fJ/conversion-step。该项工作证明自适应旁路窗逻辑和用于旁路窗逻辑的分裂-重组冗余算法这两种技术都可以有效降低电路功耗和提高电路速度。未来还可以深度挖掘振荡信息,进一步提高ADC 的动态性能,比如利用一些统计学方法得到的ENOB 甚至可以超过ADC 本身的分辨率,但这就需要对VCO-based 比较器的原理比如相位噪声等进行更深刻的分析。

A 12-bit 30-MS/s VCO-based SAR ADC with NOC-assisted multiple adaptive bypass windows

Xiangxin Pan, Xiong Zhou, Sheng Chang, Zhaoming Ding, Qiang Li

J. Semicond. 2020, 41(11): 112401

doi: 10.1088/1674-4926/41/11/112401

Full Text: http://www.jos.ac.cn/article/doi/10.1088/1674-4926/41/11/112401?pageType=en