高能效高精度SAR ADC中的误差抑制技术

作为现实模拟世界与数字世界之间的接口,模数转换器(ADC)在众多电子系统中有着广泛而关键的应用。近年来蓬勃发展的物联网技术对低成本、高能效、高精度ADC提出了巨大的需求。逐次逼近型(SAR)ADC因为其结构简单、功耗低、对先进工艺兼容性好等优势,成为近年来该领域一个非常热门的架构。然而,传统SAR难以实现高精度,这主要受限于以下几个关键的误差来源:

(1)采样噪声。长期以来,学术界公认的ADC采样噪声极限是kT/C,要想降低采样噪声,唯一的办法就是增加采样电容,然而大采样电容会给ADC的输入驱动电路和基准缓冲电路带来很大的功耗和设计复杂度。

(2)比较器噪声。比较器噪声是限制SAR ADC信噪比的最主要因素之一。降低6dB的比较器噪声,需要将比较器的功耗增大四倍,这将严重影响ADC整体的能效。

(3)数模转换器(DAC)失配。DAC会给ADC带来非线性失真的问题,限制了ADC的精度;而且,随着集成电路工艺的演进,器件尺寸越小越小,DAC失配的问题将更加严重。

近年来,清华大学电子系孙楠教授课题组提出了一系列新型ADC架构和电路技术,致力于降低SAR ADC中的这些关键误差因素,实现高能效高精度的SAR ADC。

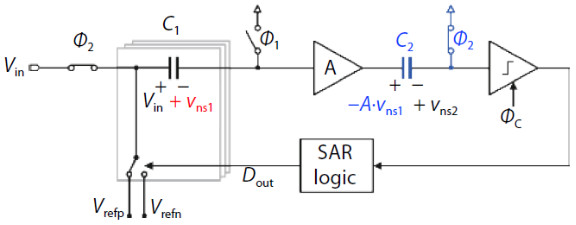

针对采样噪声的问题,孙教授课题组提出了连续时间SAR架构、kT/C噪声抵消技术、噪声频谱密度和带宽解耦技术,打破了kT/C噪声极限,使得ADC的采样电容尺寸可以大幅降低而不会带来巨大的噪声代价,进而有效缓解了输入驱动电路和基准缓冲电路的负担。

图1. 可抵消kT/C噪声的SAR ADC。

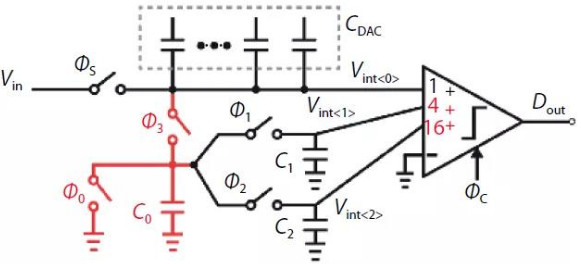

针对比较器噪声的问题,孙教授课题组提出了多种新颖的噪声整形SAR ADC技术,包括无源噪声整形、无源增益产生以及闭环动态放大器等。这些技术不依赖于传统的静态放大器就可以实现优异的噪声整形特性,具有低功耗、高PVT稳定性等特性。

图2. 无源噪声整形SAR ADC。

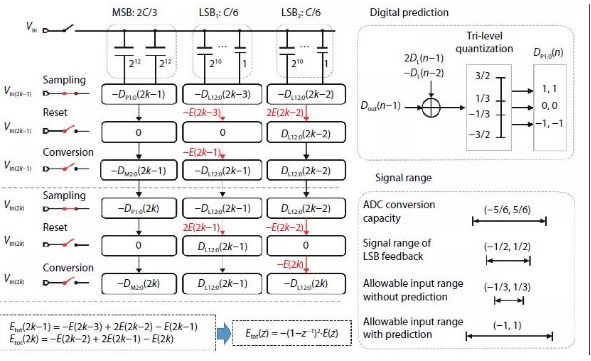

针对DAC失配的问题,孙教授课题组提出了高阶DAC失配误差整形技术,其硬件复杂度低、整形能力强,并可广泛应用于低通、高通、带通ADC中。同时,课题组还提出了用数字预测的方法来解决适配误差整形技术带来的动态范围损失的问题。

图3. 二阶DAC失配误差整形技术。

本文提出的一系列技术可有效提高SAR ADC的精度,同时保证其高能效的特性,在无线通信、物联网、生物医疗电子等领域有着广阔的应用前景。随着研究者们对该领域的持续深入研究,作者相信在将来的高精度ADC设计中,SAR将成为ΔΣ以外的一个极具吸引力的可选架构。

Error suppression techniques for energy-efficient high-resolution SAR ADCs

Jiaxin Liu, Xiyuan Tang, Linxiao Shen, Shaolan Li, Zhelu Li, Wenjuan Guo, Nan Sun

J. Semicond. 2020, 41(11): 111403

doi: 10.1088/1674-4926/41/11/111403

Full Text: http://www.jos.ac.cn/article/doi/10.1088/1674-4926/41/11/111403?pageType=en