模拟与混合信号CMOS集成锁相环芯片设计技术综述

CMOS全集成锁相环(Phase-Locked Loop, PLL)是现代片上系统(System-on-Chip, SoC)集成电路芯片中必不可少的重要组成部分,其广泛用于SoC中数字电路系统时钟生成,高速有线通信数据调制时钟生成,以及无线通信载波信号生成。近年来,随着CMOS技术的不断发展,集成电路工艺节点的持续推进,全数字锁相环(All-Digital PLL, ADPLL)开始变得流行起来。其主要原因为数字电路在先进CMOS工艺条件下具有比模拟电路更灵活的可扩展性、更好的跨工艺设计可移植性和更小的面积等优势。但是,相较于广泛应用的模拟与混合信号锁相环(Analog and Mixed-Signal PLL, AMS-PLL)而言,ADPLL由于存在量化噪声,且对电源噪声更加敏感,因此,ADPLL通常具有比AMS-PLL更高的输出信号抖动(jitter)。该问题限制了ADPLL在需要生产极低时钟抖动的应用场景中的应用,包括高性能处理器、5G无线通信、高速有线通信(比如56/112Gbps高速通信)以及下一代以太网通信等应用。因此,即使目前工艺节点尺寸已经到10nm以下,AMS-PLL依然是目前多数应用中的优先选择。

中国科学院半导体研究所张钊研究员等对AMS-PLL的基本电路结构和基本原理、主要研究问题、目前研究进展做了全面介绍,让有关科研及工程技术人员能够全面了解AMS-PLL的基础、电路设计的常见问题以及主流解决办法。同时,在全面介绍AMS-PLL的基础上,根据不同应用场景,对不同结构的AMS-PLL作了优缺点分析与对比,为有关芯片设计人员根据自身所需指标需求合理进行AMS-PLL结构选型提供参考与指导。

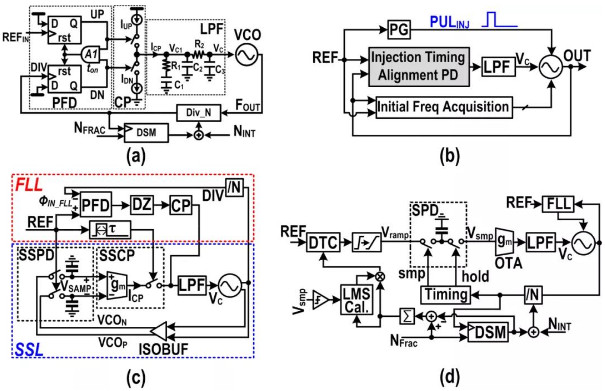

本综述论文主要包括以下内容:1、简要回顾AMS-PLL中最常用的电荷泵型锁相环(Charge-Pump based PLL, CPPLL)的基本原理;2、总结基本型CPPLL中存在的技术问题;3、系统回顾现有提升CPPLL性能的技术;4、简要介绍近年来开始成为研究热点的新型结构极低抖动AMS-PLL,包括注入锁定锁相环(Injection-Locked PLL, ILPLL)、亚采样锁相环(Sub-Sampling PLL, SSPLL)和采样锁相环(Sampling PLL, SPLL);5、分析与对比前面介绍的4种AMS-PLL结构,并据此讨论在不同应用背景下进行AMS-PLL结构选型的考虑,为有关芯片设计人员根据自身所需指标需求合理进行AMS-PLL结构选型提供参考与指导。

图1. 四种AMS-PLL电路结构框图:(a)CPPLL, (b) ILPLL, (c), SSPLL, (d)SPLL。

CMOS analog and mixed-signal phase-locked loops: An overview

Zhao Zhang

J. Semicond. 2020, 41(11): 111402

doi: 10.1088/1674-4926/41/11/111402

Full Text: http://www.jos.ac.cn/article/doi/10.1088/1674-4926/41/11/111402?pageType=en