采用四阶单环CIFB结构的18位sigma-delta开关电容调制器

目前国际最新的sigma–delta ADC研究已经达到31-bit高精度,调制阶数采用4阶或更高的5阶结构;商业化产品基本被美国ADI,TI等公司垄断,其在结构设计和工艺制造方面有长期经验积累,代表了国际ADC,DAC设计和实现的最先进水平。对比而言,国内虽然从事sigma–delta ADC的研究有多年历史,也取得了很大的进展,但应该说还基本处于跟踪阶段,大多采用2阶或3阶调制结构,精度通常在16-bit以下,与国际先进水平存在较大的差距。作者以国家863科研项目和现有成熟的勘探仪器研究工作为背景,研究高精度高阶sigma–delta ADC,以期实现有效位高于16-bit的高阶sigma–delta ADC。

sigma–delta ADC性能进步的关键在于前端模拟调制器噪声调制性能,这一方面可以通过提高调制器的阶数达到,另一方面可以通过提高量化器的位数达到。提高调制器阶数将大大降低系统稳定性,故产生了MASH结构调制器,然而由于制造工艺的限制,MASH结构中多级之间的不匹配将造成噪声性能的降低;提高量化器位数则将同时加大调制器结构的非线性,也会大大降低噪声调制性能。故sigma–delta ADC的研究方向集中于如何设计出稳定性高的高阶调制器结构,如何在保证一定非线性的条件下增加量化器位数,以及对匹配不敏感的MASH结构调制器结构开发等方面。从目前研究来看,随着调制器阶数的增加,稳定性迅速降低,故高阶结构调制器一般只用于低动态范围的环境下,更多的是在现有的低阶结构下调整调制器的反馈结构增加噪声调制性能,其次则是对MASH结构的研究,随着集成电路工艺的发展,对于MASH结构的研究逐渐流行。

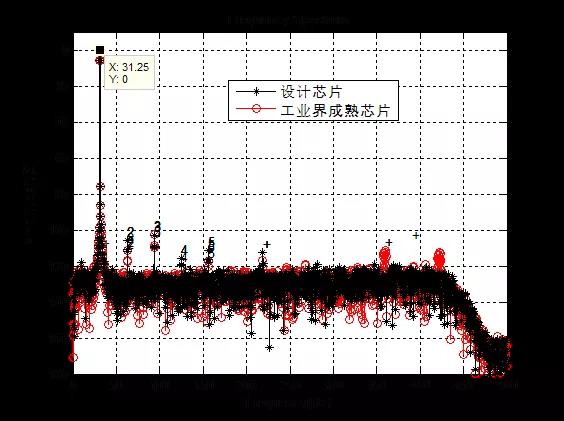

合肥高速机器视觉研究中心董宁等基于Chartered 0.35 μm CMOS工艺,成功完成一款有效位近18-bit单环4阶1位CIFB型sigma–delta模拟调制器的设计工作,芯片已成功流片,从测试结果来看,各项指标达到了设计要求。论文针对单环高阶sigma–delta调制器的设计实现进行了广泛的讨论和分析,对调制器各构成单元:运算放大器,比较器,时钟产生电路,带隙基准等设计给出了详细的电路级设计。测试结果分析表明所设计芯片达到了设计目标,其调制性能达到甚至超过了工业界成熟调制芯片。由于测试源精度的限制,目前测试所得调制器有效位为18-bit。

Sigma–delta ADC的研究应该是ADC领域最为活跃的一个分支,这主要归功于集成电路工艺技术的飞速发展,使得速度换精度的策略可以很好的应用,另一方面也是应无线通信,雷达应用以及数字音视频等领域的需求。sigma–delta ADC由于其高精度被广泛应用于以上各种领域中,尤其在石油,天然气资源勘探领域。

An 18-bit sigma –delta switched-capacitor modulator using 4-order single-loop CIFB architecture

Guiping Cao, Ning Dong

J. Semicond. 2020, 41(6): 062404

doi: 10.1088/1674-4926/41/6/062404

Full Text: http://www.jos.ac.cn/article/doi/10.1088/1674-4926/41/6/062404?pageType=en