高速负电容FinFET SRAM位单元的变化容限

在人工智能热潮下,各种物联网技术、智能设备的应用场景日益俱增,对高速,高性能,低功耗芯片的需求也在不断增长。凭借其高速和易于使用的优势,静态随机存取存储器(SRAM)已广泛应用于片上系统(SOC)。在众多的SOC以及功能要求较高的MCU中,嵌入式SRAM在芯片面积上的占比日益增大,这导致了整个芯片的性能越来越取决于SRAM的性能。摩尔定律随着工艺节点的不断减小而走向边缘,当技术节点下降至一定的工艺节点以下,器件已无法完全按照等比例缩小的原则进行设计,相邻晶体管之间的临近效应问题也随之日益增多,从而导致超大规模集成电路的稳定性以及可靠性严重受限,工艺节点的降低,低功耗的需求,芯片集成度的提高,性能速度的提升,晶体管的设计由于以上几点准则之间的相互制衡而变得日益困难。而NC-FinFET的出现,有效的改善了目前存在的问题,它是在与FinFET相同结构的基础上在栅绝缘层覆盖铁电薄膜,可以在不改变传统晶体管中载流子传输机制的情况下实现小于60 mV/dec的SS从而达到减少漏电流,提高晶体管的on-state 电流,该特性使得NC-FinFET在SRAM上有着客观的应用前景。

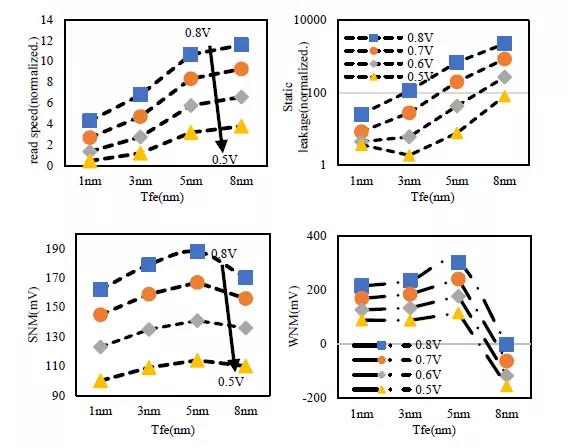

对于由NC-FinFET组成的SRAM的研究甚少,对于由工艺引起的波动性研究更是稀缺,中国科学院大学钱雅倩等针对SRAM的四个特性,静态噪声容限(SNM),写余量(WM),读取速度以及漏电流四个方面,研究了在铁电厚度,Fin的数量、温度以及工艺中影响最大的沟道长度波动的情况下,以上四个参数的变化趋势。下图就是随着铁电材料的厚度的变化,各参数所受的影响。

将NC-FinFET应用于SRAM中,将会大幅度的提升芯片的噪声容限,在不增加器件面积的情况下,有效的改善芯片的性能,高速的开关性更是能加块芯片的运行速度。NC-FinFET SRAM最吸引人的一点无疑是它的低功耗,与现有SRAM相比,其功耗降低了两个量级,这在高速低功耗的众多人工智能芯片中有着广阔的应用前景,而其真正的投产使用还有待成熟的理论以及工艺,因此本文的研究将对今后的投片试用有一定的参考价值。而后续的工作也可在此基础上继续进行研究,关于其余的波动性更是可以作更深的探讨。

Variation tolerance for high-speed negative capacitance FinFET SRAM bit cell

Yaqian Qian, Shushan Qiao, Rongqiang Yang

J. Semicond. 2020, 41(6): 062403

doi: 10.1088/1674-4926/41/6/062403

Full Text: http://www.jos.ac.cn/article/doi/10.1088/1674-4926/41/6/062403?pageType=en