全球首款多阵列忆阻器存算一体系统

清华大学钱鹤、吴华强研究团队在国际上首次实现了基于多个忆阻器阵列的存算一体系统,在处理卷积神经网络(CNN)时的能效比图形处理器芯片(GPU)高两个数量级,大幅提升了计算设备的算力,在人工智能和物联网等领域具有广阔的应用前景。

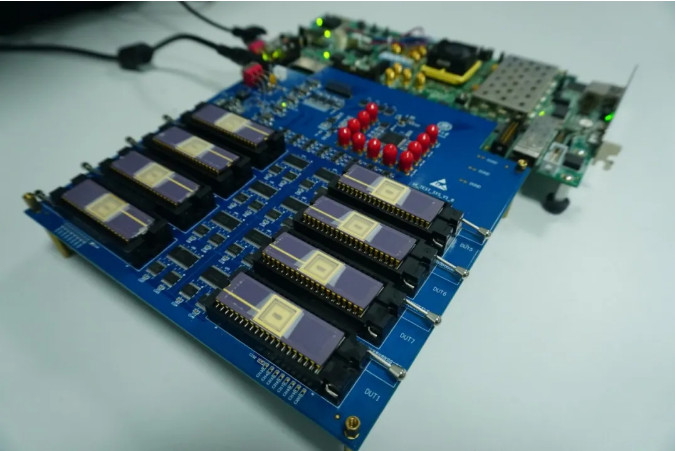

多忆阻器阵列芯片硬件系统

随着人工智能应用对计算和存储需求的不断提升,如何通过计算存储一体化突破AI算力瓶颈,成为近年来国内外的研究难点。基于忆阻器的新型存算一体架构,可以打破算力瓶颈,满足人工智能等复杂任务对计算硬件的高需求。该团队针对忆阻器在器件性能优化和工艺集成中面临的瓶颈问题,提出一种采用热保护层调控氧空位分布的新机制,进而研制出一种具有高可靠性的新型忆阻器件,并解决了CMOS工艺兼容性问题,实现了忆阻器的大规模集成。该团队进一步针对存算一体架构在处理CNN时面临的精度下降和速度失配等问题,提出一种新型混合训练方法,在系统层次克服器件非理想特性带来的精度损失,在手写数字集(MNIST)上的识别精度达到96.19%;再结合空间并行机制,将卷积核复制到多组忆阻器阵列中,提高了并行度,实现了系统加速。在此基础上,成功验证了存算一体架构全硬件实现的可行性。

该研究成果以“Fully hardware-implemented memristor convolutional neural network”为题于2020年1月29日在线发表在nature上。清华大学微电子所吴华强教授是本论文的唯一通讯作者。

详情请点击论文链接: https://www.nature.com/articles/s41586-020-1942-4

(来源:《半导体学报》微信公众号)