半导体所在片上光互连网络节点用光学路由器研究中获重要进展

随着通过提高主频来提升微处理器性能的方式遭遇“功耗之墙”的限制,多核并行处理的架构逐渐成为高性能微处理器性能继续提升的重要手段之一。对多核处理器而言,其整体性能不仅与它集成的处理核心的性能及数目有关,也极大地受制于各处理核心之间的通信效率。现有的多核处理器采用由金属连线构建的片上网络来实现多处理核心间的数据交换。基于电互连的片上网络需要在CMOS芯片中占用多层金属布线,随着片上集成的处理核心越来越多,多核处理器对片上网络通信带宽的要求越来越高,传统金属连线实现的片上网络因其高功耗、低带宽及高延迟而逐渐成为多核处理器发展的一个瓶颈。

国际半导体技术发展路线图明确指出,需要尽快找到替代电互连片上网络的新技术。光互连以其低功耗、高带宽与低延迟被广泛认为是一个非常有前景的替代方案。美国与欧盟于2008年分别启动了“基于纳米光子学的高性能芯片上通信研究”和“CMOS电路上波分复用光互连系统”的项目。国际著名计算机公司Intel、IBM、HP和SUN等也纷纷设立光子学研究部门来启动相关的研究计划。

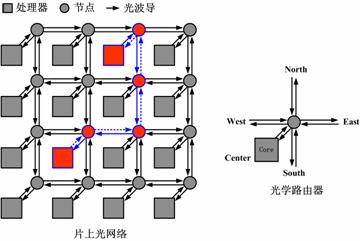

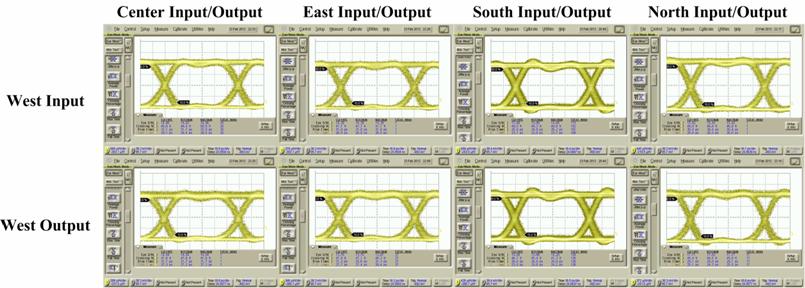

片上光互连网络节点用光学路由器的结构示意图及高速数据传输实验结果。

光学路由器是片上光互连网络的核心器件,其基本功能是实现本地节点与东、南、西、北四个方向相邻节点的数据路由和交换。美国IBM、Intel、HP、SUN、MIT、Cornell大学、Columbia大学与欧洲的IMEC、Ghent大学等著名研究机构均开展了相关研究。半导体研究所光电系统实验室自2009年开始从事片上光互连网络节点用光学路由器的研究,创新性地提出了综合性能(器件损耗、通道串扰、信道均匀性及可扩展性)优于国际同行的光学路由器的拓扑结构。经过两年的刻苦攻关,该研究小组于2011年5月率先在国际上实现了片上光互连网络节点用五端口光学路由器,其数据吞吐量为50Gbit/s(之前仅有美国Cornell大学和Columbia大学的联合小组和半导体所的研究小组先后实现了四端口光学路由器)。相关研究成果发表在著名光学期刊Optics Express九月的连续两期上。

论文链接:

四端口光学路由器(Optics Express, Vol. 19, Issue 20, pp. 18945-18955 (2011)):

http://www.opticsinfobase.org/oe/abstract.cfm?uri=oe-19-20-18945

五端口光学路由器(Optics Express, Vol. 19, Issue 21, pp. 20258-20268 (2011)):

http://www.opticsinfobase.org/abstract.cfm?uri=oe-19-21-20258